معماريات المعالجات الصغرية: خاصية أنابيب التجزئة Pipelining

تساهم تقنية أنابيب التجزئة في توفير وسيلة عملية يمكن عبرها تسريع تنفيذ التعليمات المختلفة عبر المعالج الحاسوبي بدون الحاجة لتغيير العتاد أو إضافة أنوية معالجة أخرى

1. توطئة: ما الذي نعرفه عن المعالج؟

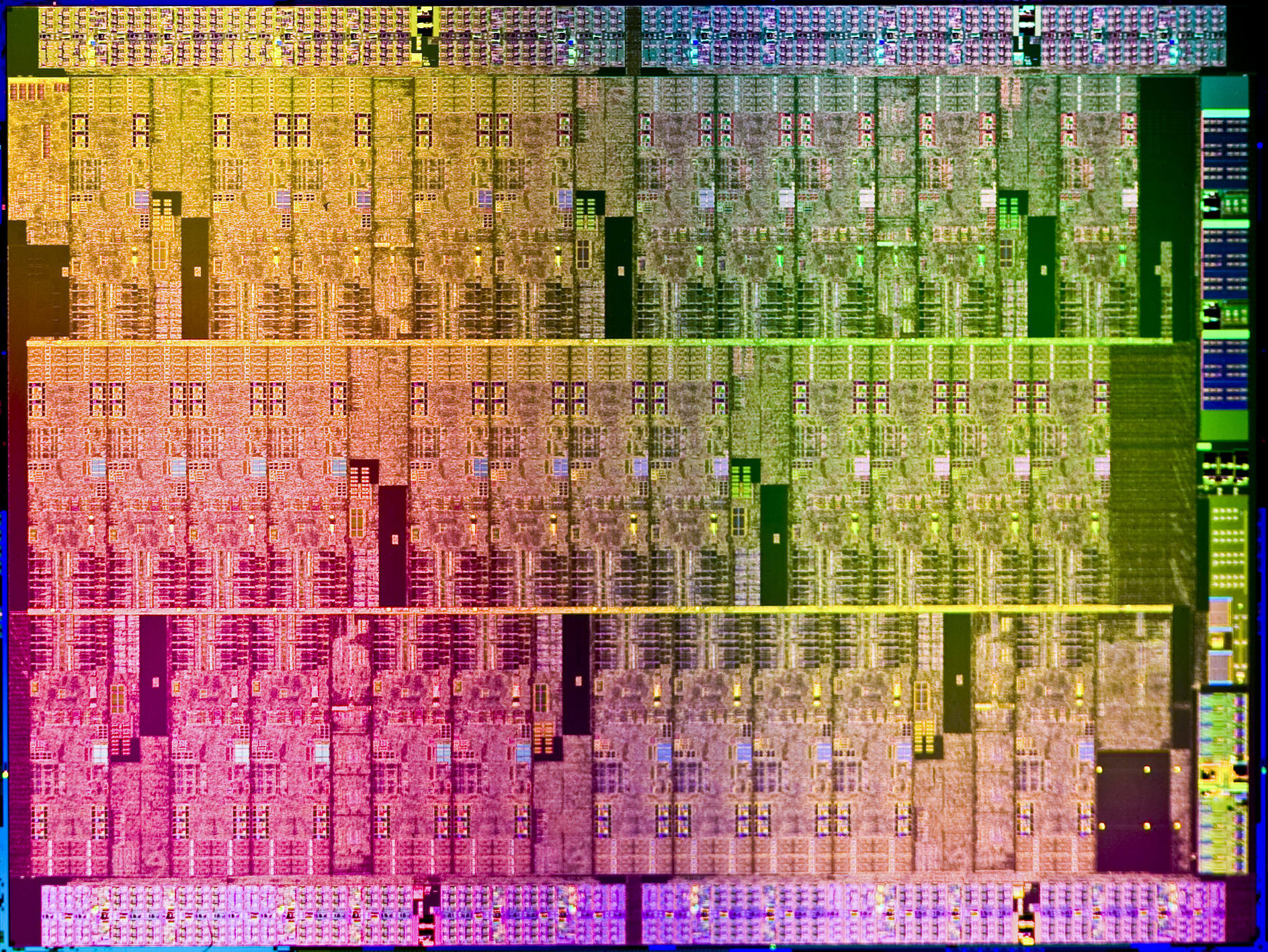

تعرفنا ضمن مقالاتٍ سابقة على مفاهيم مرتبطة بكيفية عمل المعالج الحاسوبي من الناحية التنظيمية، أي كيف يتم تبادل التعليمات بين وحدة المعالجة المركزية والذواكر، ووجدنا أن الآلية التي تحدد كيفية تنظيم حزمة التعليمات الخاصة بالمعالج هي ما يعرف باسم المعمارية Architecture أو المعمارية الصغرية Microarchitecture.

تطرقنا أيضاً إلى الأنواع المختلفة من المعماريات ووجدنا أن بعضها يرتبط بشكلٍ مباشر بتصميم عتاد المُعالج، مثل معمارية فون نيومان ومعمارية هارفرد، وهنالك معماريات أخرى ترتبط ببنية التّعليمات المُختارة كمعمارية CISC ومعمارية RISC.

- اقرأوا أيضاً: معماريات المعالجات الصغرية: ما هو الفرق بين معمارية CISC ومعمارية RISC؟

- اقرأوا أيضاً: معماريات المعالجات الصغرية: ما هو الفرق بين معمارية فون نيومان ومعمارية هارفرد

وإلى جانب هذه المعماريات، طوّر المُهندسون وعلماء الحاسوب عدداً من التّقنيات والخواص بغرض رفع سرعة الحواسيب عند مُعالجة عددٍ كبير من التّعليمات وتطبيق عدد كبير من المهام، بحيث يتم استثمار بنية المعالج وآلية عمله على أفضل نحوٍ ممكن بما يضمن تنفيذ سريع للتعليمات. إحدى أشهر هذه التقنيات هي أنابيب التجزئة Pipelining والتي هي محور هذا المقال.

2. دورة تنفيذ التعليمات Instruction Execution Cycle

أولاً، لنراجع المهام التي يقوم بها المعالج عند تلقي تعليمة ما:

- جَلب التعليمة: أي الحصول على نسخة من التعليمة المطلوب تنفيذها من الذاكرة.

- فك شيفرة التّعليمة: قراءة المسجلات وتجهيز الأنظمة المناسبة لتطبيق التعليمة في الخطوات اللاحقة.

- تشكيل العناوين: حساب العنوان المُناسب للمعامل وفقاً لمحتوى التعليمة.

- جلب المعامل: وهذا ما يمثل عملية القراءة READ operation.

- تطبيق التعليمة.

- تخزين المُعامل: وهذا ما يمثل عملية الكتابة WRITE operation، أي كتابة البيانات الناتجة في الذاكرة.

- توليد عنوان التعليمة التالية.

يجب التنويه أن هذه الخطوات لا تَعكس عدد دورات ساعة المعالج لتنفيذ التعليمة، أي لا تحتاج كل تعليمة إلى سبع دورات ليتم إنجازها. حيث أنه كما رأينا في معمارية هارفرد يتم قراءة التعليمة والمُعامل في دورةٍ واحدة ويتم تطبيق مُحتوى التعليمة في دورة أخرى. على صعيدٍ آخر، ولو أردنا اختصار العملية، فإنه يمكن القول أن دورة تنفيذ التعليمات عبارة عن ثلاث خطوات أساسية:

- مرحلة جلب التعليمة المراد تنفيذها Fetch

- مرحلة فك تشفير التعليمة المراد تنفيذها Decode

- مرحلة تنفيذ التعليمة Execute

يوجد طريقتان أساسيتان لتنفيذ سلسلة من هذه المهام. تُدعى الطريقة الأولى بـ “التنفيذ المتتالي Sequential Execution “وعبر هذه الطريقة يقوم المعالج بتنفيذ المهام السابقة بشكلٍ كامل بدءاً من أول تعليمة ومن ثم ينتقل إلى التّعليمة التي تليها ووصولاً لآخر تعليمة، ومن ثم يُعيد العملية السابقة وهكذا. أما الطريقة الثانية فهي تُدعى “أنابيب التجزئة Pipelining” وهي الخاصية المتواجدة في أغلب الحواسيب اليوم.

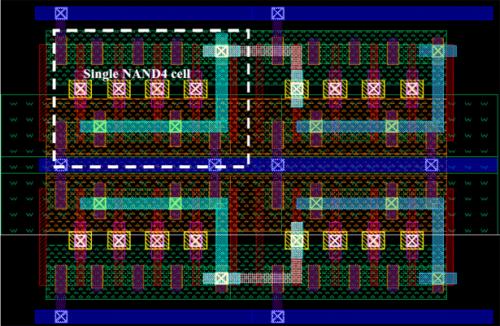

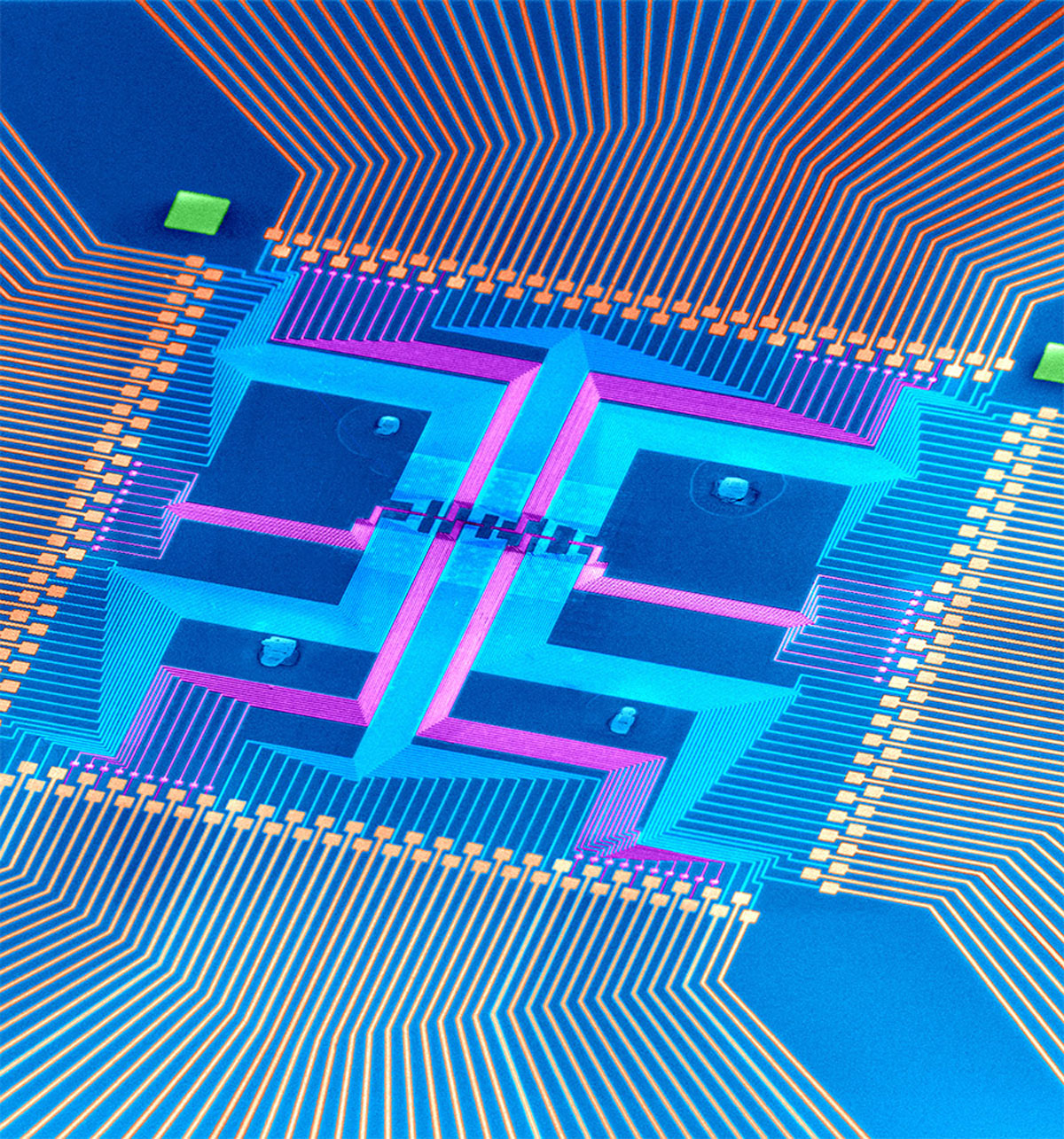

3. أنابيب التجزئة Pipelining

تأتي المساهمة الأهم لهذه الخاصية في قدرتها على تأمين طريقة يُمكن للمعالج من خلالها البدء بمهمةٍ جديدة دون الانتهاء من المهمة التي يعمل عليها. فلنتكلم بلغة الدورات، لنفرض أن تطبيق كل تعليمة يحتاج ثلاث دورات، دورة لجلب التعليمة (Fetch) من الذاكرة، دورة لقراءتها (Read) ودورة لتطبيق محتواها (Write). باستخدام خاصية أنابيب التجزئة Pipelining ستُختصر الدورات الثلاث، حيث أنه في البداية سيتم جلب التعليمة الأولى وعند قراءتها سيتم جلب التعليمة الثانية وعند التطبيق سيتم قراءة التعليمة الثانية وجلب التعليمة الثالثة وهكذا. يوضح الجدول التالي هذه الخاصية بشكلٍ أبسط لبرنامج يتألف من أربع تعليمات.

|

T5 |

T4 |

T3 |

T2 |

T1 |

T0 |

Instructions/Cycles |

|

WriteA |

ReadA |

FetchA |

A |

|||

|

WriteB |

ReadB |

FetchB |

B |

|||

|

WriteC |

ReadC |

FetchC |

C |

|||

| WriteD |

ReadD |

FetchD |

D |

نلاحظ أنه لو تم تطبيق البرنامج بشكل متتالي لاحتجنا إلى 12 دورة أي ثلاث دورات لكل تعليمة، لكن وبفضل هذه التقنية احتاج البرنامج 6 دورات فقط لإنهائه بشكل كامل. إذاً الفكرة الأساسية من مفهوم أنابيب التجزئة في معماريات المعالجات الصغرية، هي أنه لا يوجد داعي أن يتم انتظار انتهاء تنفيذ تعليمةٍ ما بشكلٍ كامل، كي تم البدء بتعليمةٍ ثانية، وهذا الأمر سيسمح باختصار عدد دورات ساعة المعالج اللازمة من أجل تنفيذ كل التعليمات.

هنالك أمر هام يجب ذكره فيما يتعلق بأنابيب التجزئة: لنفرض مثلاً أن عملية حاسوبية ما تتطلب زمناً قدره 1 نانوثانية كي يتم إنجازها. ولنفرض أنه يوجد لدينا 10 تعليمات كل منها تتطلب 1 نانوثانية كي يتم تنفيذها. لو تم تنفيذ هذه التعليمات بشكلٍ تسلسلي بحيث يتم تنفيذ الثانية عندها نهاية تنفيذ الأولى، فإن هذا الأمر يعني أن زمن التنفيذ الكلي لـ 10 تعليمات سيكون 10 نانوثانية. الآن، فإن ما تقوم به أنابيب التجزئة فعلياً هو تجزيء التعليمة نفسها التي تتطلب 1 نانوثانية إلى عدة أجزاء، وعندما يبدأ المعالج بتنفيذ التعليمة الأولى، لن ينتظر حتى انتهائها كلياً ليبدأ بالثانية، بل سيبدأ بالجزء الأولى من التعليمة الثانية أثناء تنفيذ الأولى، وسيبدأ بالجزء الأول من التعليم الثالثة أثناء تنفيذ أجزاء التعليمة الثانية، وسيبدأ بأول جزء من التعليمة الرابعة أثناء تنفيذ أجزاء التعليمة الثالثة…وهكذا. هذا الأمر سيعني اختصار الوقت الكلي اللازم لتنفيذ 10 تعليمات حاسوبية، إلا أن زمن تنفيذ التعليمة الواحدة سيبقى 1 نانو ثانية، ولا يمكن تغيير هذا الزمن، إلا بتغيير طريقة تنفيذ التعليمة نفسها، أي تسلسل جلب الأوامر من الذاكرة وتنفيذها ومن ثم إعادة تخزينها، وهو الأمر الذي لا تتدخل به أنابيب التجزئة.

4. علاقة المعمارية بأداء المعالج

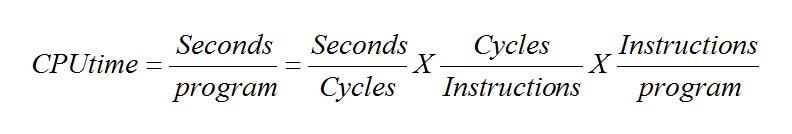

تٌستخدم المعادلة الشهيرة التالية لقياس أداء وكفاءة المعالج:

إذاً يعتمد أداء وحدة المعالجة المركزية CPU على عد التّعليمات Instruction Count، عدد الدورات التي تحتاجها التعليمة الواحدة Cycles Per Instruction CPI وزمن الدورة الواحدة، ويتم التحكم في هذه العوامل الثلاث بحسب بُنية المعمارية المتعلقة بمجموعة التّعليمات Instruction Set Architecture. المَنهجية في معمارية CISC تقوم على اختصار عدد التّعليمات ضمن البرنامج لكن بمقابل الزّيادة في عدد دورات التّعليمة الواحدة. على عكس ذلك، في معمارية RISC يتم اختصار عدد الدورات للتعليمة الواحدة مقابل الزيادة في عدد التّعليمات ضمن البرنامج.

إذاً يعتمد أداء وحدة المعالجة المركزية CPU على عد التّعليمات Instruction Count، عدد الدورات التي تحتاجها التعليمة الواحدة Cycles Per Instruction CPI وزمن الدورة الواحدة، ويتم التحكم في هذه العوامل الثلاث بحسب بُنية المعمارية المتعلقة بمجموعة التّعليمات Instruction Set Architecture. المَنهجية في معمارية CISC تقوم على اختصار عدد التّعليمات ضمن البرنامج لكن بمقابل الزّيادة في عدد دورات التّعليمة الواحدة. على عكس ذلك، في معمارية RISC يتم اختصار عدد الدورات للتعليمة الواحدة مقابل الزيادة في عدد التّعليمات ضمن البرنامج.

وبالمقابل سوف نبحث عن العتاد المناسب للحصول على معالجات عالية الكفاءة. كما ذكرنا في مقال سابق، تعتمد آلة فون نيومان على دمج ذاكرة البرنامج وذاكرة البيانات ضمن ذاكرة واحدة مشتركة مما يجعل التركيبة بين معمارية فون نيومان ومعمارية CISC أسوأ خيار من جانب الكفاءة بسبب تعقيد تعليمات معمارية CISC واحتياج التعليمة الواحدة إلى عدة دورات. من جهة أخرى، تسمح لنا آلة هارفرد بجلب التّعليمة ضمن دورة واحدة، ونحتاج أيضاً إلى جورة واحدة لقراءة التعليمة في معمارية RISC بسبب بساطة التعليمات، مما يجعل الدمج بين المعماريتين الخيار الأنسب للحصول على حواسيب بكفاءة عالية.

أضاف المُصممون خاصية أنابيب التجزئة إلى ذلك الدمج بهدف رفع سرعة وكفاءة عمل المعالجات، حيث أنه من السهل تطبيق هذه الخاصية على عتاد هارفرد بسبب وجود ذاكرة البرنامج بشكلٍ مُنفصل عن ذاكرة البيانات مما يسمح للمعالج العمل على عدد من المهام في الوقت ذاته.

5. خلاصة

6. مصادر إضافية للاطلاع

- كتاب “High Performance Computer Architecture” من تأليف “هارولد س. ستون Harold S. Stone”.

- مقال تعليمي من جامعة ستانفورد حول خاصية أنابيب التجزئة

- مقال تعليمي من موقع Engineers Garage حول خاصية أنابيب التجزئة