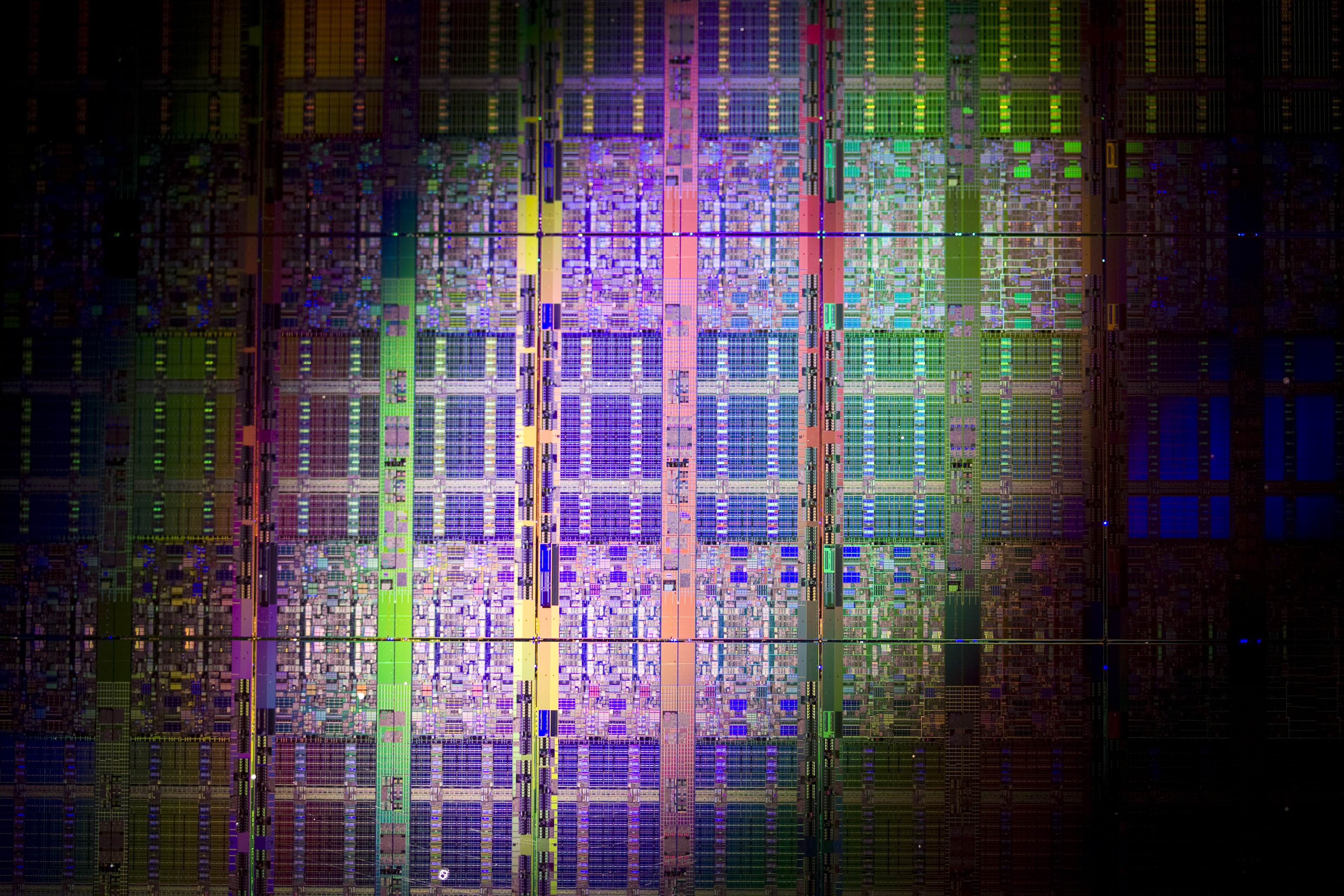

ترانزستورات الرقائق النانوية المتراكبة: فكرة إنتل الجديدة للمحافظة على قانون مور

كشفت شركة إنتل عن مبدأ تصميميّ جديد يعتمد على ترانزستورات الرقائق النانوية، والذي من شأنه المساعدة في تكديس الترانزستورات على الشرائح بشكلٍ مستمر والمحافظة على قانون مور

إنتل، الترانزستور وقانون مور

تعتمد الدارات المنطقية في الأجهزة الرقمية التي نستخدمها اليوم على اقتران نوعين من الترانزستورات هما ترانزستور موسفيت ذو القناة السالبة NMOS وترانزستور موسفيت ذو القناة الموجبة (موسفيت MOSFET هو اختصار لترانزستور تأثير المجال ذو الأكسيد المعدني). تمتلك بوابة كل من هذين الترانزستورين قطبية كهربائية مختلفة، وهذا يعني أن إشارة الجهد الكهربائي التي تؤدي لتشغيل أحدهما ستؤدي إلى إيقاف تشغيل الآخر، وبالتالي فإن وضعهما معاً بشكلٍ متجاوز يُشير إلى أن التيار الكهربائي سيمر فقط في حال حصول تغير بقيمة البت ما يقلل من استهلاك الطاقة إلى حد كبير. لقد تم وضع هذان الزوجان على نحو متجاور طوال عقود خلت، لكن التطور التقني يفرض تقليص حجم الدارات الكهربائية؛ وبالتالي تقريب المسافة بين الترانزستورات لأقصى درجة ممكنة.

تقريب المسافات بين الترانزستورات هو أمرٌ هام، لأنه يتيح تكديس عدد أكبر من الترانزستورات على الشريحة الواحدة، ومع زيادة عدد الترانزستورات على الشريحة فإن أداء المعالجة سيكون أفضل، وهذا سيضمن أننا سنحصل على حواسيب ذات أداء أفضل بشكلٍ مستمر. لخص الشريك المؤسس لشركة إنتل جوردون مور بتنبؤه الشهير الذي أصبح يُعرف اليوم باسم قانون مور، والذي يقول أن عدد الترانزستورات على الشريحة يجب أن يتضاعف مرة واحدة كل سنتين (تقريباً). تمكنت إنتل (وغيرها من شركات تصنيع شرائح المعالجة) من المحافظة على هذا المبدأ لعقودٍ خلت، إلا أن الواقع اليوم يُشير إلى أن المحافظة على قانون مور والاستمرار بدفع قدرات المعالجة يتطلب تغييرتٍ جذرية بطرق تصنيع المعالجات، وعندما نقول “تصنيع المعالج” فإن المقصود هنا هو تصنيع ترانزستورات موسفيت ودارات سيموس التي تشكل وحدات البناء الأساسية لعمليات المعالجة التي تتم داخل المعالج.

لهذا السبب تسعى شركة إنتل جاهدة لتطوير طرق تصنيع الترانزستورات بما يضمن المحافظة على إمكانية تضمين عدد أكبر من الترانزستورات في الشرائح الإلكترونية بشكلٍ مُستمر، وكشفت الشركة مؤخراً خلال “الاجتماع الدولي للأجهزة الإلكترونية IEDM” عن طريقة مختلفة لوضع الترانزستورات وتجميعها، تمثلت في تركيبهما فوق بعضهما. ساهمت هذه الطريقة بحسب إنتل بتقليص حجم دارة سيموس إلى النصف، وبالتالي مضاعفة كثافة الترانزستور في الدارات المتكاملة التي سيتم إطلاقها في المستقبل.

ترانزستورات الرقائق النانوية بدلاً من ترانزستورات فين-فيت

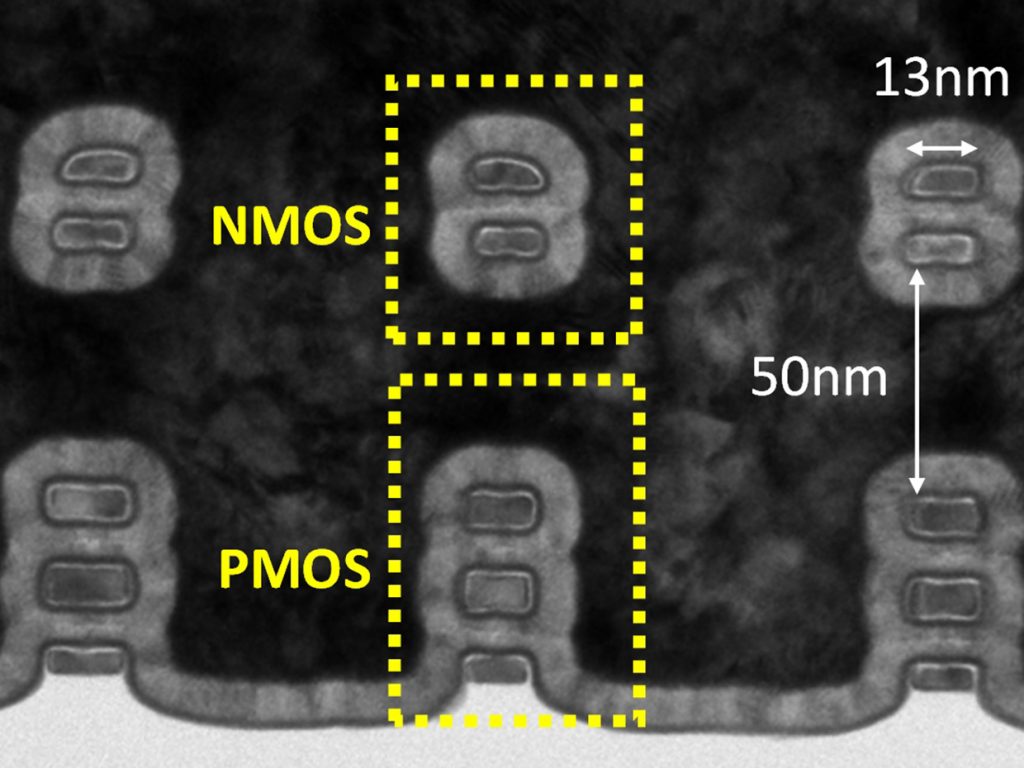

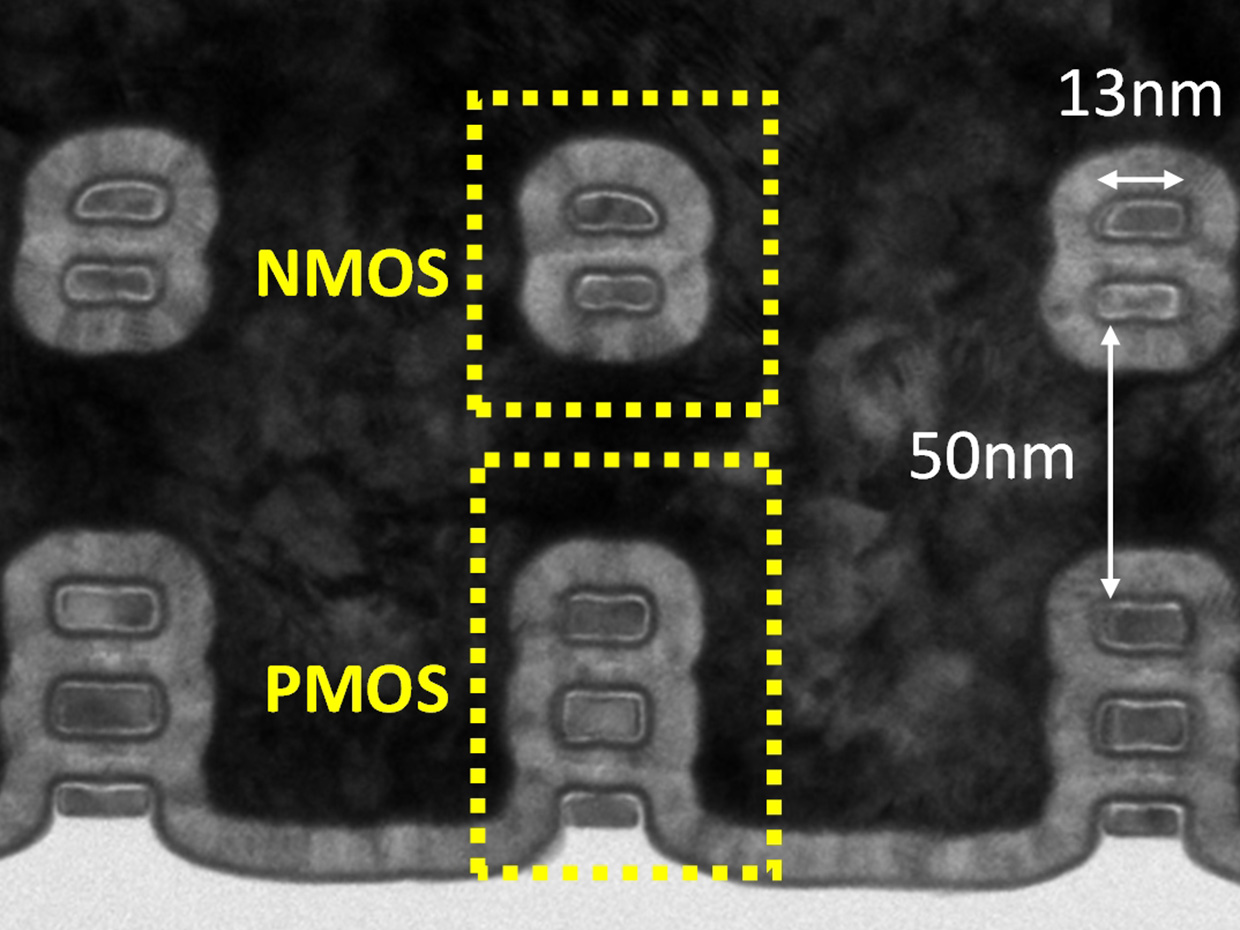

تعتمد الفكرة على استخدام البنية التي يُنظر لها على نطاق واسع أنها الجيل المقبل لبنية الترانزستور: ترانزستورات الرقائق (الشرائح) النانوية. تعتمد إنتل في الوقت الحاليّ على بنية تُدعى “فين-فيت FinFET” من أجل تصنيع الترانزستورات المستخدمة في صناعة شرائح المعالجة، والفكرة الأساسية من هذه التقنية هي استخدام زعنفة عمودية من السليكون التي ستجعل الترانزستور ذو عدة بوابات (ولذلك يُطلق عليها ببعض الأحيان الأجهزة متعددة البوابات). بالنسبة للفكرة الجديدة، أي ترانزستورات الشرائح النانوية، فإنها تعتمد على بنية مختلفة: بدلاً من الجزء الرئيسي من الترانزستور والمكون من زعنفة Fin عمودية من السيليكون، فإن قناة الرقاقة النانونية تتكون من عدة صفائح رقيقة بسماكة نانوميتر متكدسة أفقياً فوق بعضها.

استخدم مهندسو شركة إنتل هذه الأجهزة لتصميم دارة العاكس المنطقي “الإنفرتر Inverter“، وهي أبسط بنية لدارات سيموس المنطقية. يحتاج عمل دارة الإنفرتر إلى ترانزستورين، سلكين متصلين بالطاقة، ووصلة إدخال ووصلة إخراج. وفي حال تركيب الترانزستورات على نحو متجاور – كما هو حال الدارات اليوم – يكون التركيب مضغوطاً للغاية، لكن طريقة وضع الترانزستورات فوق بعضها وتعديل مكان الوصلات الداخلية تساعد في تقليص مساحة دارة الإنفرتر إلى النصف.

التراصف الذاتي: تركيب ترانزستورين معاً خلال نفس الوقت

يطلق على فكرة إنتل التي تتمحور حول بناء شرائح نانونية فوق بعضها اسم “عملية التراصف الذاتي Self-Aligned Process ” لأنها تعتمد على تركيب الجهازين في نفس الخطوة. ويعتبر ذلك مهماً لأن إضافة خطوة جديدة مثل تركيبها على رقائق منفصلة ثم توصيل الرقائق معاً من شأنه التسبب باختلالٍ في التموضع أو محاذاة غير صحيحة قد تدمر أي دارات محتملة.

تتمحور العملية حول تعديل الخطوات المتبعة في تركيب الترانزستورات النانونية، إذ تبدأ مع رصف طبقات متتالية من السيليكون والجرمانيوم السيليكوني، ثم يتم نحتها لتأخذ شكل زعنفة Fin ضيقة وطويلة، ومن ثم يتم إجراء إزالة Etching أجزاء من الجرمانيوم السيليكوني بما سيؤدي بالنتيجة لترسب وبقاء مجموعة من رقائق السليكون النانوية. عادةً ما تشكل جميع الصفائح النانونية ترانزستور واحد، لكن في هذه الحالة، ترتبط الصفيحتان النانويتان العلويتان بالسيليكون المُشاب بالفوسفور لتشكيل ترانزستور موسفيت ذو القناة السالبة NMOS ، في حين، ترتبط الصفيحتان السفليتان بالجرمانيوم السيليكوني المُطعّم بالبورون لتشكيل ترانزستور موسفيت ذو القناة الموجبة PMOS.

تشكل عملية “تدفق التكامل Integration Flow” آلية أكثر تعقيداً، لكن الباحثون في إنتل عملوا جاهدين لتبسيطها قدر الإمكان، وقد أوضح ذلك السيد روبرت تشاو، الزميل الأساسي في شركة إنتل ومدير أبحاث المكونات لديها، بقوله: “لا يمكن أن نعقّد عمل تدفق التكامل لأن ذلك سيؤثر على التطبيق العملي لصنع الرقائق باستخدام دارة سيموس ذات الترانزستورات المتراصفة، وتُعطي هذه العملية الفعالة النتائج المرجوة”.

- اقرأوا أيضاً: ما بعد قانون مور – الحصول على الحوسبة النانوية

بمجرد أن نعتاد على الشكل الجديد، ستتمثل الخطوة التالية في متابعة الأداء والذي يشتمل تحسين عمل ترانزستور موسفيت ذو القناة الموجبة PMOS، الذي لا يماثل قدرة ترانزستور موسفيت ذو القناة السالبة NMOS من ناحية تمرير التيار الكهربائي. من المُرجح أن حل هذه المشكلة يتمثل في إدخال الجهد ضمن قناة الترانزستور، وتتمحور الفكرة حول تشويه شبكة بلورات السيليكون بطريقةٍ تجعل حاملات الشحن (الثقوب في هذه الحالة) تتدفق بسرعة. يعود إدخال إنتل لقيم الجهد في أجهزتها إلى عام 2002، وقد أظهرت إنتل خلال بحث منفصل عرضته في الاجتماع الدولي للأجهزة الكهربائية طريقةً جديدةً لإنتاج الجهد الانضغاطي ومطاوعة الشد في الترانزستورات النانونية.

إنتل ليست وحدها

تسعى مؤسسات بحثية أخرى إلى إتمام تصاميم الصفائح النانونية المكدسة والتي يطلق عليها في بعض الأحيان “ترانزستورات تأثير المجال المُكملة CFET: Compelementary FET” ويُعتبر معهد الأبحاث البلجيكي للإلكترونيات الدقيقة Imec رائداً في مجال أبحاث ترانزستور تأثير المجال، وقد كشف عن تصميمه هذه الأنواع خلال ندوة معهد مهندسي الكهرباء والإلكترونيات التي تناولت دارة التكامل الفائق في يونيو الماضي، لكن المكونات لم يتم تصنيعها من ترانزستورات الشرائح النانوية بشكل كامل، بل تكونت الطبقة السفلية من ترانزستور تأثير المجال FinFET بينما كانت الطبقة العلوية عبارة عن رقاقة نانونية مفردة. كشف باحثون من تايوان في هذا السياق عن إمكانية إنتاج ترانزستورات تأثير المجال المكملة CFET ذات بنية تعتمد على رقاقة نانوية منفردة لكل من ترانستورات القناة السالبة NMOS والموجبة PMOS. بالمقارنة مع ذلك، تحتوي دارة إنتل رقاقتين علويتين من ترانزستور موسفيت ذو القناة السالبة NMOS، وثلاث رقائق نانونية من ترانزستور موسفيت ذو القناة الموجبة، وهو الشكل الأقرب للفكرة المفترضة مستقبلاً.

المصدر: [IEEE Spectrum]

تعليق واحد