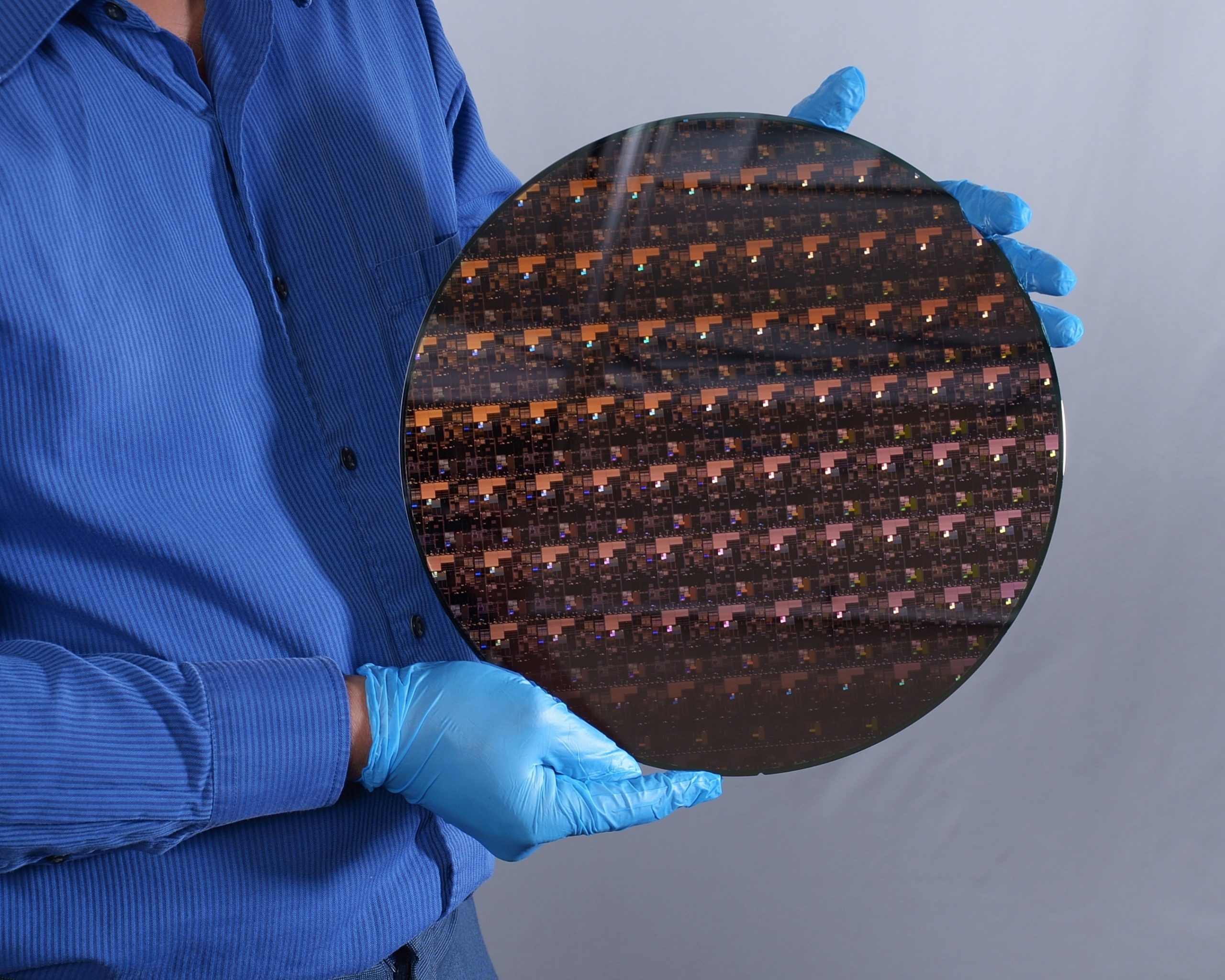

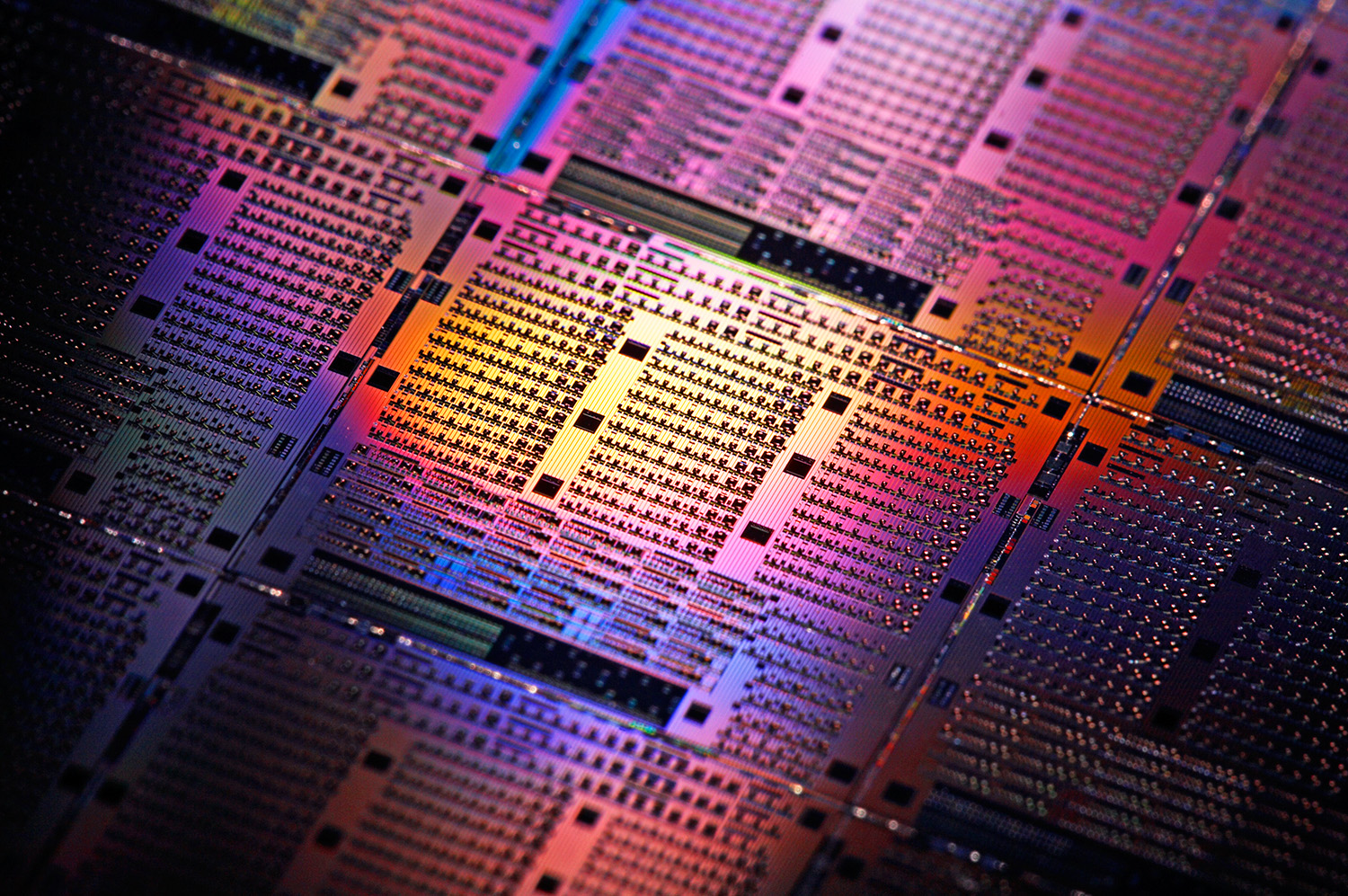

[سبق تقني]: آي بي إم تُطلق أول شريحة معالجة بدقة تصنيع 2 نانومتر

أصبحت شركة آي بي إم الأميركية أول شركة في العالم تتمكن من تصنيع شريحة معالجة حاسوبية بتقنية تصنيع بدقة 2 نانومتر، متفوقة على كل الشركات الأخرى في هذا المجال.

تمثل الترانزيستورات وحدات البناء الأساسية في شرائح المعالجة الحاسوبية، حيث يتكون المعالج – من حيث المبدأ – من عددٍ هائلٍ من الترانزيستورات، ووظيفة هذه الترانزيستورات هي تشكيل الدارات المنطقية المختلفة التي تقوم بمهام المعالجة وتخزين البيانات. الفكرة الأساسية هنا أنه كلما تناقص حجم الترانزيستور نفسه، كلما أمكن تضمين شريحة المعالجة بعددٍ أكبر من الترانزيستورات بدون الحاجة لزيادة مساحة الشريحة، ما يعني الحصول على قدرات حاسوبية أكثر دون الحاجة لبناء معالجات ضخمة. إن كنتم ممن يتابع أخبار المعالجات الحاسوبية، ستعلمون أن شركة مثل إنتل تعاني من أجل تجاوز عتبة التصنيع بدقة 10 نانومتر، وأن أفضل ما يتوفر حالياً في السوق هو معالج M1 من آبل الذي تم تصنيعه بدقة 5 نانومتر، وبالتالي فإن إعلان آي بي إم عن شريحة بدقة 2 نانومتر هو حدثُ من شأنه ضمان تطور شرائح المعالجة ومستقبل الصناعة التقنية بشكلٍ عام.

- اقرأوا أيضاً: كل ما تريد معرفته عن المعالجات الصغرية

ما الذي يعنيه الحصول على تقنية تصنيع بدقة 2 نانومتر؟

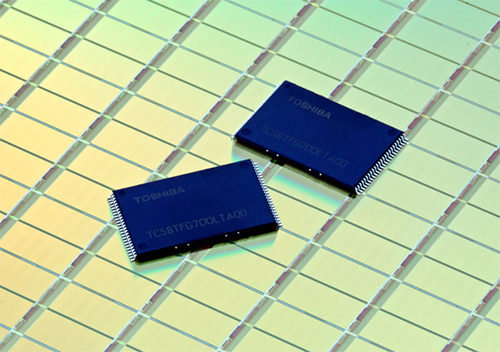

بحسب التصريح الرسمي من شركة آي بي إم، وعبر استخدام تقنية التصنيع الجديدة سيكون بالإمكان تصنيع شرائح معالجة حاسوبية قادرة على تحسين أداء المعالجة بحوالي 45% عند استهلاك نفس كمية الطاقة الكهربائية، أو استهلاك طاقة كهربائية أقل بنسبة 75% مع المحافظة على نفس الأداء الذي توّفره الشرائح المصنوعة بتقنية 7 نانومتر. عبر استخدام تقنية التصنيع بدقة 2 نانومتر، وبحسب آي بي إم، سيكون بالإمكان تضمين 50 مليار ترانزيستور ضمن شريحة معالجة لا تتجاوز مساحتها ظفر الإصبع.

من أجل فهم التقدم الذي ستوّفره الشرائح المصنوعة بدقة 2 نانومتر، وللابتعاد عن الجدل المتعلق بمعنى “التصنيع بدقة 7 أو 5 أو 3 نانومتر”، يمكن اللجوء للجدول الذي قام موقع AnandTech بإعداده، والذي يُقارن كثافة الترانزيستورات ضمن الشرائح بحسب تقنيات المعالجة من الشركات المختلفة، وهو كما يلي:

| الشركة | دقة التصنيع | كثافة الترانزيستورات (مليون ترانزيستور / ميللي متر مربع) |

| إنتل Intel | 14 نانومتر | 45 |

| إنتل Intel | 10 نانومتر | 100 |

| إيه إم دي AMD – TSMC | 7 نانومتر | 91 |

| إنتل Intel | 7 نانومتر | 237 |

| آبل Apple – TSMC | 5 نانومتر | 171 |

| آي بي إم IBM | 2 نانومتر | 333 |

اعتماداً على المعلومات التي يوّفرها الجدول السابق سنلاحظ أمرين هامين: يختلف معنى “دقة التصنيع” بين الشركات بشكلٍ كبير، فدقة تصنيع 7 نانومتر من إنتل من المتوقع أن توفر كثافة ترانزيستورات قدرها 237 مليون ترانزيستور لكل ميللي متر مربع، بينما نفس دقة التصنيع من إيه إم دي توفر كثافة قدرها 91 مليون ترانزيستور لكل ميللي متر مربع. بكل الأحوال، وما يهمنا هنا هو تقنية 2 نانومتر من آي بي إم، والتي من المنتظر أن توّفر كثافة عالية تبلغ 333 مليون ترانزيستور لكل ميللي متر مربع، ما يعني حوالي ضعف ما توّفره أفضل التقنيات المتوفرة حالياً، وهي تقنية التصنيع بدقة 5 نانومتر من شركة TSMC والتي تستخدمها آبل في معالجات M1 الخاصة بها.

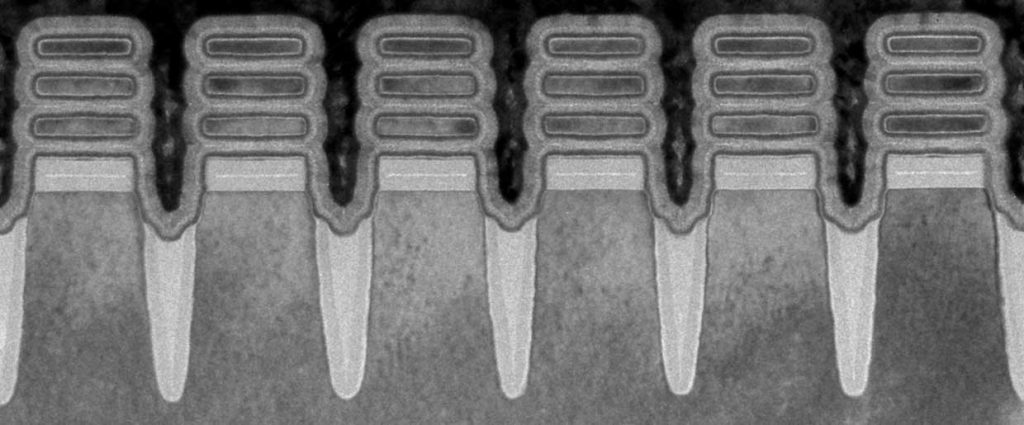

المبدأ التقني: ترانزيستورات الرقائق النانوية المتراكبة

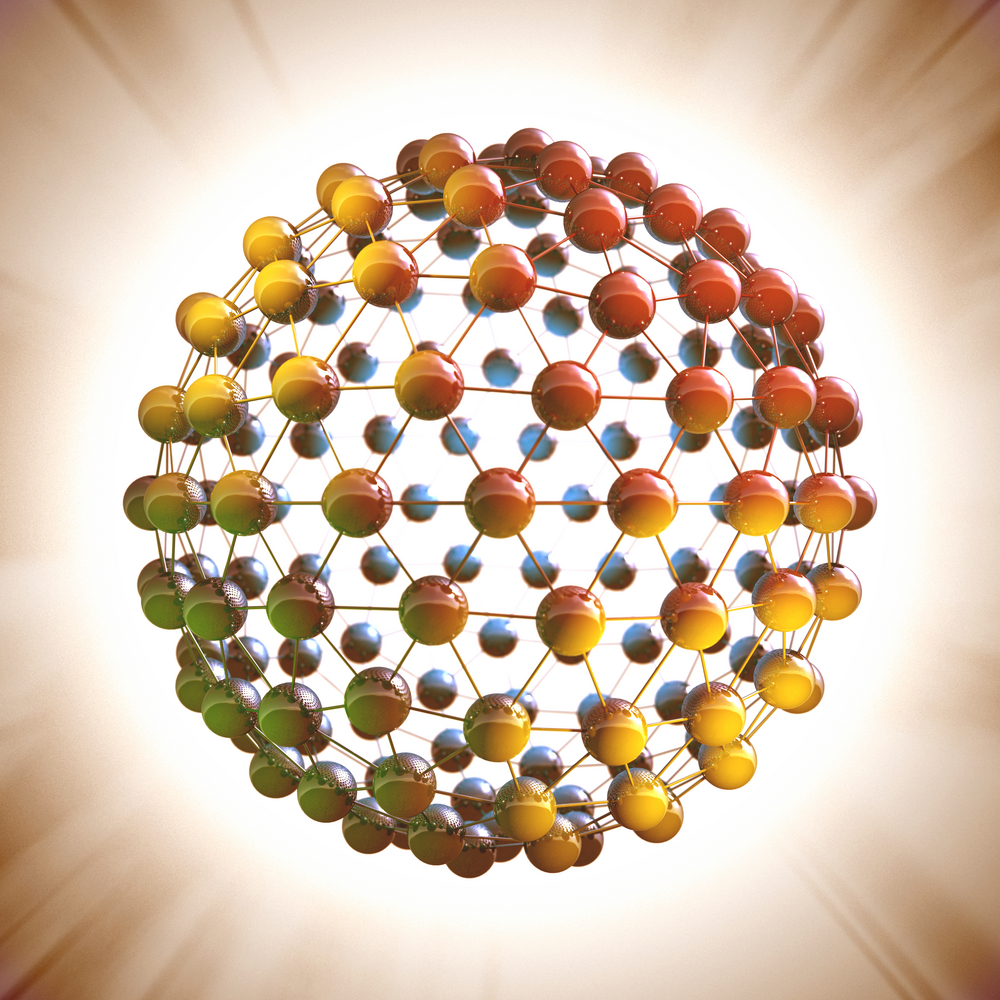

قامت آي بي إم ببناء الشريحة الجديدة اعتماداً على تقنية ترانزيستورات الرقائق النانوية المتراكبة، وهذا يعني أن كل ترانزيستور يتكون من ثلاث طبقات أفقية من رقائق السيليكون المتوضعة فوق بعضها البعض، وتكون سماكة كل طبقة عدة نانومترات، ومن ثم يتم إحاطة هذه الطبقات جمعياً ببوابة. ومن المنتظر أن تستبدل تقنية ترانزيستورات الرقائق النانوية تقنية فين-فيت FinFet، والتي من المتوقع ألا تكون مناسبة لتصنيع الشرائح عند دقة تصنيع تتجاوز 7 نانومتر؛ عند دقة أقل من 7 نانومتر سيكون من الصعب التحكم بالخواص الكهربائية للترانزيستورات (الفتح والإغلاق Switch On/Off) وسيحصل تسرب للإلكترونات من الترانزيستور نفسه ما يُساهم بنشوء تيارات تسريب عالية Leak-Currents.

ابتكارات متعددة في سبيل تصنيع الشريحة الجديدة

في سبيل تصنيع الشريحة بدقة 2 نانومتر، استخدمت آي بي إم تقنياتٍ هي الأولى على الصعيد الصناعي والتقني، مثل استخدام تقنية العزل الكهربائي القاعي BDI: Bottom-Dielectric Isolation لإنتاج بوابات بطول 12 نانومتر (المرة الأولى في هذا المجال)، وبما يُساهم بتحسين مشكلة التسريب الفرعي للقناة Sub-Channel Leakage وكذلك تحسين الأداء من ناحية استهلاك الطاقة. الأمر الثاني الهام هنا هو استخدام آي بي إم لتقنية الطباعة الحجرية المعتمدة على الأشعة فوق البنفسجية الشديدة EUV: Extreme-Ultraviolet Lithography من أجل تشكيل وحفر البُنى الخاصة بالعناصر الإلكترونية والكهربائية (الترانزيستورات، المقاومات، المكثفات..الخ) مباشرةً على المواد نصف الناقلة، أو ما يُعرف باسم FEOL: Front-end-of-Line. أخيراً قامت آي بي إم بتطوير جهد عتبة متعدد Multi-Threshold-Voltage بما يتناسب مع التطبيق الذي ستستخدم من أجله الشرائح المصنوعة بتقنية 2 نانومتر، وبالتحديد، تم تطوير جهد العتبة المتعدد من أجل تطبيقات الأنظمة على شريحة SoC وتطبيقات الحوسبة عالية الأداء High-Performance-Computing.

الأفق المستقبلية

تعتقد آي بي إم أن الشريحة الجديد ستوفر آفاق جديدة بالنسبة للأنظمة الحاسوبية التي تستخدمها آي بي إم وكذلك بالنسبة للشركات الأخرى التي قد تستخدم هذه التقنية، وأحد الأمور الهامة هو إمكانية تخفيض البصمة الكربونية Carbon-Footprint من مراكز معالجة البيانات Data Centers، والتي تُعتبر من أكبر مستهلكي الطاقة حول العالم ما يعني تسببها بإطلاق كميات كبيرة من غاز ثاني أوكسيد الكربون. قدرت آي بي إم أنه وفي حال قيام مراكز البيانات باعتماد شرائحة معالجة بدقة 2 نانومتر (بدلاً من شرائحها الحالية) فإن هذا الأمر سيوفر طاقة كهربائية لأكثر من 43 مليون منزل.

على صعيد الإلكترونيات الاستهلاكية، قامت آي بي إم بإطلاق وعودٍ أقل ما يمكن القول عنها أنها “كبيرة”: ستؤمن شرائح المعالجة المصنوعة بدقة 2 نانومتر تحسيناً في استهلاك الطاقة بمعدل 4 مرات بالمقارنة مع شرائح 7 نانومتر، وهذا يعني أن مستخدمي الهواتف الذكية سيكونوا قادرين على شحن بطاريات هواتفهم مرة كل بضعة أيام، بدلاً من مرة كل يوم (على الأقل). لا يقتصر الأمر عل ذلك، بل تؤكد آي بي إم أن شرائح المعالجة بدقة 2 نانومتر ستؤمن معالجة أسرع للبيانات تتناسب مع سرعات الإنترنت العالية التي ستوفرها شبكات الجيل الخامس والسادس، كما أنها ستلعب دوراً كبيراً في مجال السيارات ذاتية القيادة عبر تحسين القدرات الحاسوبية في مجال الإبصار الحاسوبي والتعرف على البيئة المحطية بالسيارة على نحو أسرع وأكثر دقة.

متى ستكون هذه التقنية متوفرة؟ تقول آي بي إم أنه من المتوقع البدء بإنتاج شرائح معالجة جاهزة للاستخدام التجاري والمعتمدة على تقنية 2 نانومتر بحلول بداية سنة 2024.